# (19) 대한민국특허청(KR)

### (12) 등록특허공보(B1)

(51) Int. Cl.

HO1L 21/336 (2006.01) HO1L 21/20 (2006.01) HO1L 21/027 (2006.01) B82Y 40/00 (2011.01)

(21) 출원번호

10-2008-0084554

(22) 출원일자

2008년08월28일

심사청구일자

2008년08월28일

(65) 공개번호

10-2010-0025836

(43) 공개일자

2010년03월10일

(56) 선행기술조사문헌

KR1020070102633 A\*

JP2005125428 A

KR1020070099462 A

US7278324 B2

\*는 심사관에 의하여 인용된 문헌

(45) 공고일자 2011년07월19일

(11) 등록번호 10-1050142

(24) 등록일자 2011년07월12일

(73) 특허권자

#### 한국과학기술연구원

서울 성북구 하월곡동 39-1

(72) 발명자

#### 변영태

경기도 구리시 교문동 1번지 8호 동방아파트 101-1604

### 김선호

서울특별시 종로구 평창동 177-15 (뒷면에 계속)

(74) 대리인

이학수, 한라특허법인, 백남훈

전체 청구항 수 : 총 16 항

심사관: 권순근

#### (54) 나노선 다중채널 FET 소자의 제조방법

#### (57) 요 약

본 발명은 나노선 다중채널 FET 소자의 제조방법에 관한 것으로서, 기존 나노물질 FET 소자들의 한계를 극복하여 높은 전류 전송 능력과 빠른 전하 이동도를 동시에 구현하는 나노선 다중채널 FET 소자를 저비용으로 대량생산할 수 있는 제조방법에 관한 것이다. 이러한 본 발명은, 나노선 다중채널 FET 소자의 제조 방법에 있어서, 포토리소그라피와 습식식각 공정을 통해 기판 또는 기판 위 박막에 V 홈 나노선 배열을 형성하는 단계와; 용액 공정을 통해 상기 V 홈 나노선 배열의 V 홈 내에 나노물질을 자기조립하는 단계와; 상기 나노물질이 자기조립된 V 홈 나노선 배열을 이용하여 다중채널 FET 소자를 제조하는 단계;를 포함하는 것을 특징으로 한다.

### 대 표 도 - 도6

(72) 발명자

이석

22-908

서울특별시 서초구 반포동 1-1 신반포아파트

전영민

서울특별시 강남구 청담동 102-1 효성빌라 26-303

#### 특허청구의 범위

#### 청구항 1

나노선 다중채널 FET 소자의 제조 방법에 있어서,

- (a) 포토리소그라피와 습식식각 공정을 함께 이용하여 기판 또는 기판 위의 박막에 V 홈 나노선 배열을 형성하는 단계와;

- (b) 상기 V 홈 나노선 배열이 형성된 기판을 나노물질 용액에 담구어 V 홈 내부에 나노물질을 자기조립하는 단계와;

- (c) 상기 나노물질이 자기조립된 V 홈 나노선 배열을 이용하여 다중채널 FET 소자를 제조하는 단계;

를 포함하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 2

청구항 1에 있어서,

상기 V 홈 나노선 배열을 형성하는 상기 기판 또는 기판 위 박막 물질은 Si, SOI(Silicon-On Insulator), GOI(GaAs-On Insulator), IOI(InP-On Insulator), GaAs, InP, 및 이를 기반으로 성장되는 Ⅲ-V 화합물 단결정 반도체 중 선택된 것임을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 3

청구항 1에 있어서,

상기 (a) 단계에서,

포토리소그라피 공정으로 제조된 반복적인 포토레지스트 직선 패턴의 폭이 2  $\mu$ m 이하이면서 직선 패턴 사이의 간격이 2  $\mu$ m 이하이고,

포토리소그라피 공정에서 반복적인 직선 패턴의 수가 임의로 조절될 수 있는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 4

청구항 1에 있어서,

상기 (a) 단계에서,

포토리소그라피 공정으로 제조된 반복적인 포토레지스트 직선 배열이 화학적인 습식식각(chemical wet etching) 용액을 통해 이방성 식각이 되어 V 홈이 형성되는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 5

청구항 4에 있어서,

상기 습식식각 공정에서 사용되는 식각 마스크의 물질은 포토레지스트(photoresist),  $SiO_2$ ,  $Si_3N_4$ , 폴리머 (polymer), 및 금속 박막 중 선택된 것임을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 6

청구항 4에 있어서,

상기 습식식각 공정으로 제조된 V 홈의 식각깊이가 3  $\mu$  이하인 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 7

청구항 1에 있어서,

상기 (a)단계는,

- (al) 포토리소그라피 공정으로 제작된 반복적인 포토레지스트 직선 패턴들을 포함하는 기판을 OTS(octadecyltrichlorosilane) 용액에 담구어 OTS 박막을 상기 기판 표면에 증착시키는 단계와;

- (a2) 포토레지스트를 제거하여 반복적인 OTS 패턴이 형성되고 이에 OTS 패턴 사이에서 기판이 노출되도록 하는 단계와;

- (a3) OTS 박막을 식각 마스크로 사용하는 습식식각 공정을 통해 상기 기판에 V 홈 나노선 배열을 형성하는 단계;

를 포함하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 8

청구항 7에 있어서,

실리콘 기판이 사용될 때 V 홈이 형성되면 폭방향에 대한 깊이방향의 식각률이 400배 이상으로 커지면서 식각이 중지되도록 하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 9

청구항 7에 있어서,

실리콘 기판이 사용될 때 V 홈이 형성되는 식각시간을 측정하여 V 홈이 형성되기 전에 하단면의 선폭을 식각시간으로 조절하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 10

청구항 7에 있어서,

상기 (a1) 단계에서,

기판을 OTS 용액에 담구는 시간은 중착된 OTS 박막의 두께가 0.5 ~ 1.5  $\mu$ m의 범위가 되도록 결정되는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 11

청구항 7에 있어서,

상기 (a3) 단계 다음에는,

(a4) 상기 V 홈 나노선 배열이 형성된 기판을 APTES(3-aminopropyl trimethoxysilane) 용액에 담구어 V 홈 내부에 APTES 박막을 증착시키는 단계;

를 더 포함하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 12

청구항 11에 있어서,

상기 (a4) 단계는,

상기 기판의 V 홈 내부에서 높이에 따라 APTES의 농도가 다른 APTES 박막을 형성하며,

상기 기판을 나노물질 용액 속에 담구어 상기 V 홈의 폭방향으로 한 개의 나노물질이 정렬되도록 하는 것을 특 징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 13

청구항 11 또는 청구항 12에 있어서,

상기 V 홈에 APTES 박막을 증착시키는 과정에서 기판을 APTES 용액에서 꺼낸 뒤 평평한 바닥에 놓아두어 APTES 용액이 V홈 내부 벽면을 따라 흘러내리도록 함으로써 APTES의 농도가 V 홈 내부에서 아래쪽으로 내려갈수록 증가되도록 하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 14

청구항 1에 있어서.

상기 다중채널 FET 소자를 제조하기 위한 기판 재료가 SOI 웨이퍼이고, 상기 SOI 웨이퍼에서 V 홈 나노선 배열 이 형성되는 Si 박막은 언도프트(undoped) Si이며, SiO<sub>2</sub> 아래의 Si 기판은 백-게이트(back-gate) 전극을 형성하기 위해 도프트(doped) Si로 이루어진 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 15

청구항 14에 있어서,

상기 SOI 웨이퍼에서 V 홈 나노선 배열을 Si 박막 위에 형성할 때,

V 홈의 깊이방향에 대한 폭방향의 식각비율이 100 이하인 식각용액을 사용하여 V 홈 내부에서 그 하단의  $SiO_2$ 가 노출되도록 형성하고, 이때 노출된  $SiO_2$ 의 폭을 식각시간으로 조절하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 청구항 16

청구항 15에 있어서,

상기 V 홈의 내부에 정렬된 나노물질의 아랫면 부분이 상기 노출된 SiO<sub>2</sub> 위에 접촉되고, 상기 정렬된 나노물질의 양쪽 측면 부분은 상기 언도프트 Si에 접촉되어, 이웃하게 정렬된 나노물질들이 서로 전기적으로 고립되도록 한 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법.

#### 명 세 서

### 발명의 상세한 설명

### 기술분야

[0001] 본 발명은 나노선 다중채널 FET 소자의 제조방법에 관한 것으로서, 기존 나노물질 FET 소자들의 한계를 극복하여 높은 전류 전송 능력과 빠른 전하 이동도를 동시에 구현하는 나노선 다중채널 FET 소자를 저비용으로 대량생산할 수 있는 제조방법에 관한 것이다.

#### 배경기술

- [0002] 나노물질 중 단일벽 카본 나노튜브(Single-Walled Carborn Nanotube; SWNT)는 전자 이동도(electron mobilit y)가 높기 때문에 전계효과 트랜지스터(Field Effect Transistor; FET) 소자에 응용 가능성이 크고, 체적 대비 표면적이 크기 때문에 화학센서와 바이오센서로 응용성이 매우 크다.

- [0003] 그러나, 현재 SWNT 소자의 상용화를 막고 있는 중요한 장애물은 SWNT가 특정 위치에서 특정 방향으로 배열된 구조를 제조하는 대량 조립기술의 부재이다. 또한 소자 기판을 고온에 노출하지 않고 TFT(Thin Film

Transistor)나 FET를 다양한 기판 물질 위에 제작하기 위해서는 기존의 CVD 성장 방법 대신에 성장된 SWNT를 기판 위에 증착하는 용액 공정 기술이 확보되어야 한다.

- [0004] 상기 문제를 극복하기 위해 FET 소자에 대해서는 먼저 한 개의 SWNT가 소스(source)와 드레인(drain) 전극 사이에 채널을 형성하는 단일채널 소자가 연구되었다[문헌 1].

- [0005] 단일채널 FET 소자는 아주 높은 전자 이동도(μ>10000 c㎡/Vs)를 갖는 반면에[문헌 2], 한 개의 SWNT로 운반할 수 있는 전류의 양이 매우 작은 단점이 있다.

- [0006] 상기 문제를 회피하기 위해서 채널이 한 개의 SWNT 대신에 임의 방향(random)의 SWNT 네트워크를 이용하는 FET 소자가 연구되었다[문헌 3].

- [0007] SWNT 네트워크 FET 소자의 전하 이동도(µ)는 ~ 10 c㎡/Vs이기 때문에 단일채널 FET 소자보다 약 1000배 이상 낮다. 따라서, SWNT 네트워크보다 큰 전자 이동도를 얻기 위해서는 나노물질이 일정한 영역에서 한 방향으로 배열된 채널이 제조되어야 한다. 그리고, 단일채널 FET 소자보다 향상된 전류 운반 능력을 얻기 위해서는 단일채널 대신에 다중채널을 갖는 나노선 FET 소자가 제조되어야 한다.

- [0008] 최근에 과학적인 탐구와 공학적인 응용들이 나노미터까지 확대되고 있기 때문에, 규칙성이 좋을 뿐만 아니라 패턴, 크기, 모양이 모두 잘 조절될 수 있는 나노구조의 제작 필요성이 급증하고 있다. 많은 응용에서 나노구조들이 상당히 큰 면적에서 제조되어야 하고, 제조비용이 수용할 수 있는 범위 내에 있어야 나노구조들이 많이 쓰이게 될 것이다.

- [0010] 최근에 정렬된 나노물질 패턴을 대면적으로 만들기 위해 포토리소그라피와 탄소나노튜브의 자기조립 방법을 이용하여 선폭이 3 ~ 4  $\mu$ 에인 나노물질의 조립 패턴이 보고되었다[문헌 4].

- [0011] 그러나, 용액 공정에서 사용되는 탄소나노튜브는 직경이 수 nm이고 길이가 1 ~ 2 \(\mu\mi\m)이기 때문에 폭방향으로 한 개의 나노튜브로 배열된 패턴을 제조하는 것이 현실적으로 불가능하다.

- [0012] 따라서, 단일채널 FET 소자보다 큰 전류 운반 능력과 무작위 네트워크(random network) FET 소자보다 큰 전하 이동도를 동시에 얻기 위해서는 나노물질이 조립되는 선폭이 sub-micron 이하로 더 작아져야 한다.

- [0013] (참고)

- [0014] [문헌 1] J. Kong, N. Franklin, C. Zhou, M. Chapline, S. Peng, K. Choi, H. Dai, "Nanotube Molecular Wires as Chemical Sensors," Science, Vol. 287, p. 622(2000).

- [0015] [문헌 2] Xinjian Zhou, Ji-Yong Park, Shaoming Huang, Jie Liu, and Paul L. McEuen, "Band Structure, Phonon Scattering, and the Performance Limit of Single-Walled Carbon Nanotube Transistors," Phys. Rev. Lett., 95, p. 146805(2005).

- [0016] [문헌 3] E. S. Snow, J. P. Novak, P. M. Campbell, and D. Park, "Random networks of carbon nanotubes as an electronic material," Appl. Phys. Lett., Vol.82, No. 13, pp. 2145(2003).

- [0017] [문헌 4] M. Lee, J. Im, B. Y. Lee, S. Myung, J. Kang, L. Huang, Y.-K. Kwon & S. Hong, "Linker-free directed assembly of high-performance integrated devices based on nanotubes and nanowires" *Nanotechnology*, Vol.1, p.66 (2006).

#### 발명의 내용

#### 해결 하고자하는 과제

[0018] 본 발명은 기존의 실험실 수준에서 지적 호기심을 충족하기 위해 개발되어온 나노물질을 이용하는 FET 소자 및 이를 이용한 화학센서와 바이오센서에서 나타나는 문제점을 해결하기 위한 수단을 제공하는데 그 목적이 있다.

- [0020] 기존의 실험실 수준에서 지적 호기심을 충족시키기 위해 개발되어온 나노구조 물질을 이용하는 FET 소자가 상용화되기 위해서는 현재의 반도체 산업과 호환성이 있는 기술을 이용하여 저비용과 대면적의 생산공정이 구축되어야 한다. 그리고, 이 기술이 적용된 나노물질의 FET 소자는 높은 전하 이동도와 큰 전류 운반 능력이 동시에 충족되어야 한다. 이에 본 발명은 높은 전하 이동도와 전류 운반 능력을 동시에 충족하고 저비용과 대면적으로 나노물질 FET 소자를 제조할 수 있는 방법을 제공하고자 하는 것이다.

#### 과제 해결수단

- [0021] 상기한 목적을 달성하기 위해, 본 발명은, 나노선 다중채널 FET 소자의 제조 방법에 있어서, 포토리소그라피와 습식식각 공정을 통해 기판 또는 기판 위 박막에 V 홈 나노선 배열을 형성하는 단계와; 용액 공정을 통해 상기 V 홈 나노선 배열의 V 홈 내에 나노물질을 자기조립하는 단계와; 상기 나노물질이 자기조립된 V 홈 나노선 배열을 이용하여 다중채널 FET 소자를 제조하는 단계;를 포함하는 것을 특징으로 하는 나노선 다중채널 FET 소자의 제조방법을 제공한다.

- [0022] 바람직한 실시예에서, 상기 V 홈 나노선 배열을 형성하는 상기 기판 또는 기판 위 박막 물질은 Si, SOI(Silicon-On Insulator), GOI(GaAs-On Insulator), IOI(InP-On Insulator), GaAs, InP, 및 이를 기반으로 성장되는 Ⅲ-V 화합물 단결정 반도체 중 선택된 것임을 특징으로 한다.

- [0023] 또한 상기 포토리소그라피와 습식식각 공정을 통해 V 홈 나노선 배열을 형성하는 단계에서,

- [0024] 포토리소그라피 공정으로 제조된 반복적인 포토레지스트 직선 패턴의 폭이 2  $\mu$ m 이하이면서 직선 패턴 사이의 간격이 2  $\mu$ m 이하이고,

- [0025] 포토리소그라피 공정에서 반복적인 직선 패턴의 수가 임의로 조절될 수 있는 것을 특징으로 한다.

- [0026] 또한 상기 포토리소그라피와 습식식각 공정을 통해 V 홈 나노선 배열을 형성하는 단계에서,

- [0027] 포토리소그라피 공정으로 제조된 반복적인 포토레지스트 직선 배열이 화학적인 습식식각(chemical wet etching) 용액을 통해 이방성 식각이 되어 V 홈이 형성되는 것을 특징으로 한다.

- [0028] 또한 상기 습식식각 공정에서 사용되는 식각 마스크의 물질은 포토레지스트(photoresist), SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, 폴리머 (polymer), 및 금속 박막 중 선택된 것임을 특징으로 한다.

- [0029] 또한 상기 습식식각 공정으로 제조된 V 홈의 식각깊이가 3 μm 이하인 것을 특징으로 한다.

- [0030] 또한 포토리소그라피 공정을 통해 제작된 반복적인 포토레지스트 직선 패턴들을 포함하는 기판을 OTS(octadecyltrichlorosilane) 용액에 담구어 OTS 박막을 증착시키고,

- [0031] 이어 포토레지스트를 제거하여 반복적인 OTS 패턴이 형성되고 이에 OTS 패턴 사이에서 기판이 노출되도록 하며,

- [0032] 이어 OTS 박막을 식각 마스크로 사용하는 습식식각 공정을 통해 상기 기판에 V 홈 나노선 배열을 형성하고,

- [0033] 상기 V 홈 나노선 배열이 형성된 기판을 나노물질 용액에 담구어 나노물질을 V 홈 내에 정렬시키는 용액 공정을 실시하는 것을 특징으로 한다.

- [0034] 또한 실리콘 기판이 사용될 때 V 홈이 형성되면 폭방향에 대한 깊이방향의 식각률이 400배 이상으로 커지면서 식각이 중지되도록 하는 것을 특징으로 한다.

- [0035] 또한 실리콘 기판이 사용될 때 V 홈이 형성되는 식각시간을 측정하여 V 홈이 형성되기 전에 하단면의 선폭을 식 각시간으로 조절하는 것을 특징으로 한다.

- [0036] 또한 상기 포토레지스트 직선 패턴들을 포함하는 기판을 OTS 용액에 담구어 OTS 박막을 증착시키는 과정에서,

- [0037] 기판을 OTS 용액에 담구는 시간은 증착된 OTS 박막의 두께가 0.5 ~ 1.5 세계의 범위가 되도록 결정되는 것을 특징으로 한다.

- [0038] 또한 포토리소그라피 공정을 통해 제작된 반복적인 포토레지스트 직선 패턴들을 포함하는 기판을 OTS 용액에 담구어 OTS 박막을 증착시키고,

- [0039] 이어 포토레지스트를 제거하여 반복적인 OTS 패턴이 형성되고 이에 OTS 패턴 사이에서 기판이 노출되도록 하며,

- [0040] 이어 OTS 박막을 식각 마스크로 사용하는 습식식각 공정을 통해 상기 기판에 V 홈 나노선 배열을 형성하고,

- [0041] 이어 상기 V 홈 나노선 배열이 형성된 기판을 APTES(3-aminopropyl trimethoxysilane) 용액에 담구어 V 홈에 APTES 박막을 중착시킨 뒤, APTES 박막이 중착된 기판을 나노물질 용액에 담구어 나노물질을 V 홈 내에 정렬시키는 용액 공정을 실시하는 것을 특징으로 한다.

- [0042] 또한 상기 기판의 V 홈 내부에서 높이에 따라 APTES의 농도가 다른 APTES 박막을 형성한 뒤 기판을 나노물질 용액 속에 담구어 상기 V 홈의 폭방향으로 한 개의 나노물질이 정렬되도록 하는 것을 특징으로 한다.

- [0043] 또한 상기 V 홈에 APTES 박막을 증착시키는 과정에서 기판을 APTES 용액에서 꺼낸 뒤 평평한 바닥에 놓아두어 APTES 용액이 V홈 내부 벽면을 따라 흘러내리도록 함으로써 APTES의 농도가 V 홈 내부에서 아래쪽으로 내려갈수록 증가되도록 하는 것을 특징으로 한다.

- [0044] 또한 상기 다중채널 FET 소자를 제조하기 위한 기판 재료가 SOI 웨이퍼이고, 상기 SOI 웨이퍼에서 V 홈 나노선 배열이 형성되는 Si 박막은 언도프트(undoped) Si이며, SiO<sub>2</sub> 아래의 Si 기판은 백-게이트(back-gate) 전극을 형성하기 위해 도프트(doped) Si로 이루어진 것을 특징으로 한다.

- [0045] 또한 상기 SOI 웨이퍼에 형성되는 V 홈은 깊이방향에 대한 폭방향의 식각비율이 100 이하인 식각용액을 사용하여 V 홈 내부에서 그 하단의 SiO<sub>2</sub>가 노출되도록 형성하고, 이때 노출된 SiO<sub>2</sub>의 폭을 식각시간으로 조절하는 것을 특징으로 한다.

- [0046] 또한 상기 V 홈의 내부에 정렬된 나노물질의 아랫면 부분이 상기 노출된 SiO<sub>2</sub> 위에 접촉되고, 상기 정렬된 나노물질의 양쪽 측면 부분은 상기 언도프트 Si에 접촉되어, 이웃하게 정렬된 나노물질들이 서로 전기적으로 고립되도록 한 것을 특징으로 한다.

#### 효 과

- [0047] 이에 따라, 본 발명에 의하면, 포토리소그라피와 습식식각의 반도체 공정 기술을 이용해 기판에 나노선 배열을 형성한 뒤 용액 공정을 이용해 단위 나노선의 폭방향으로 한 개의 나노물질을 정렬하여 나노기술이 융합된 나노 선 다중채널을 구성할 수 있으며, 이를 통해 나노선 다중채널 FET 소자를 제조할 수 있게 된다.

- [0048] 그 결과, 본 발명에 의해 제조되는 FET 소자는 기존의 나노물질 FET 소자들의 한계인 높은 전류 전송 능력과 빠른 전하 이동도를 동시에 구현할 수 있으며, 특히 나노 채널의 수가 반도체 공정으로 조절될 수 있게 됨으로써 소스-드레인의 전류 크기가 임의로 조절될 수 있어, 외부 회로에서 전류 증폭기가 필요 없게 된다.

- [0049] 또한 본 발명에서 이용되는 포토리소그라피와 습식식각 공정은 기존의 실리콘 반도체 산업과 호환성이 있기 때문에 저비용으로 대량생산이 가능한 장점이 있다. 이와 더불어, 용액 공정은 특별한 고가의 장비 없이 쉽게 대면적으로 공정을 할 수 있기 때문에 공정비가 저렴하다. 따라서, 본 발명은 V 홈 나노선 다중채널 FET 소자나 FET 소자를 기반으로 하는 나노선 다중채널 FET 어레이(array) 소자 및 상기 소자들과 구동회로가 집적된 SOC(System On Chip) 칩을 대량생산 방식으로 제조할 수 있는 방법을 제공하며, 산업상으로 이용 가능성이 매우크다.

- [0050] 본 발명에 의해 제조되는 나노선 다중채널 FET 소자는 고속과 고출력을 필요로 하는 전자소자, 논리소자, 화학 센서 및 바이오센서와 그들을 기반으로 하는 어레이 소자에 유용하게 적용이 가능하다.

### 발명의 실시를 위한 구체적인 내용

- [0051] 이하, 본 발명의 바람직한 실시예를 첨부도면을 참조로 상세하게 설명한다.

- [0052] 본 발명은 기존의 단일채널 SWNT FET 소자와 무작위 네트워크(random network) FET 소자의 문제점들을 극복하기 위해 기존의 실리콘 반도체 산업에서 잘 확립된 반도체 공정을 이용하여 저비용과 대면적으로 나노선 다중채널 FET 전자소자를 제조할 수 있는 방법을 제공한다.

- [0053] 특히, 본 발명에서는 V 홈 나노선의 반복적인 배열을 대면적 및 저비용으로 제작하기 위하여 포토리소그라피와 이방성 식각 기술을 이용한다.

- [0054] 그리고, 본 발명은 나노선 배열이 제조되는 방법과 제조된 나노선에 나노물질이 자기조립되는 방법을 제공하고, 이를 이용하여 V 홈 나노선 다중채널 FET 소자가 제조되는 방법을 제공한다.

- [0055] 우선, 포토리소그라피와 이방성 식각을 이용하여 V 홈(V groove) 나노선 배열을 형성하는 방법 및 상기 나노선 배열에 나노물질을 정렬하는 방법에 대해 설명하기로 한다.

- [0056] 기존의 포토리소그라피와 나노물질의 자기조립을 이용하여 제작된 FET 소자는[문헌 4] 채널의 폭이 3 ~ 4 /m이기 때문에 자기조립된 SWNT가 채널 폭당 1개 이상씩 배열되었다. 그 결과 높은 전류 운반 능력과 큰 전하 이동도를 동시에 향상시키지 못했다. 이 문제를 해결하기 위해서는 포토리소그라피로 1 /m 이하인 sub-micron 선폭을 제조할 수 있는 기술이 필요하다. 그러나, 포토리소그라피용 광 마스크는 선폭이 1 /m 이하가 될 때제조비용이 급상승하기 때문에 상용화에 문제가 된다.

- [0057] 상기한 문제를 해결하기 위해서 본 발명은 마이크론 패턴의 포토리소그라피 공정 후 나노선폭을 제조할 수 있는 식각 공정을 제공한다. 단결정 반도체인 Si, GaAs, InP와 이들을 기반으로 하는 화합물 반도체들은 화학 습식 식각을 하는 경우 결정방향에 따라 식각속도가 다르기 때문에 이방성 식각이 된다.

- [0058] 본 발명에서는 포토리소그라피와 습식식각 공정을 통해 기판 또는 기판 위 박막에 V 홈 나노선 배열을 형성하는 데, V 홈 나노선 배열을 형성하는 기판 또는 박막 물질로는 Si, SOI(Silicon-On Insulator), GOI(GaAs-On Insulator), IOI(InP-On Insulator), GaAs, InP 및 이를 기반으로 성장되는 III-V 화합물 단결정 반도체가 될 수 있다.

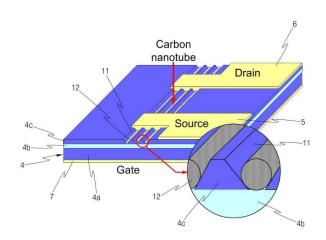

- [0059] 첨부한 도 1은 GaAs와 Si 단결정의 이방성 식각의 한 예를 보여준다. 도1의 (a)는 인산계 식각용액 (H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O = 19:6:25)에서 식각 마스크로 폭이 2 μm인 PR이 사용되었다. 이때 PR 마스크 아래의 인접한 GaAs가 에칭되기 때문에 식각깊이가 2 μm일 때 위쪽의 직선 폭(0.8 μm)이 아래쪽의 폭(3.5 μm) 보다 좁아진다. 즉, 깊이방향과 폭방향의 식각이 서로 다른 식각속도로 진행되기 때문에 이방성 식각이 된다. 도 1의 (b)는 실리콘 V 홈(도면부호 11임)이 제작되는 결정방향과 식각면의 모양을 보여준다. 이방성 식각을 위한 화학 습식식각 공정에서 식각 마스크(etch mask)의 물질로는 포토레지스트(photoresist), SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, 폴리머 (polymer), 금속 박막 등이 사용될 수 있다.

- [0060] 실리콘을 이방성 식각하기 위해서 KOH 용액이 사용될 수 있는데, 이 경우 두 가지의 장점이 있다. 첫째, 마스크 사이의 간격은 식각깊이에 따라서 더 넓어질 수 있다( $L_o \approx 1.414~t_{Si}$ ). 따라서, 식각된 하단면의 폭이 식각깊이로 조절된다. 이것은 포토리소그라피의 한계 분해능을 극복할 수 있는 수단을 제공한다. 만일 반복적으로 식각된 하단면 위에 나노물질(나노튜브나 나노와이어)이 정렬된다면 나노선을 이용한 다중채널 FET 소자가 제조될 수 있다. 둘째, KOH의 식각률이 (111) 면에 대해 매우 느리기 때문에 일단 V 홈이 실리콘에서 만들어지면 식각이 거의 멈춘다. 그 이유는 (100) 면과 (111) 면 사이의 식각비율이 400:1이기 때문이다[문헌 5].

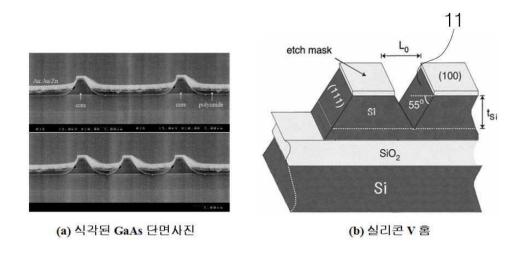

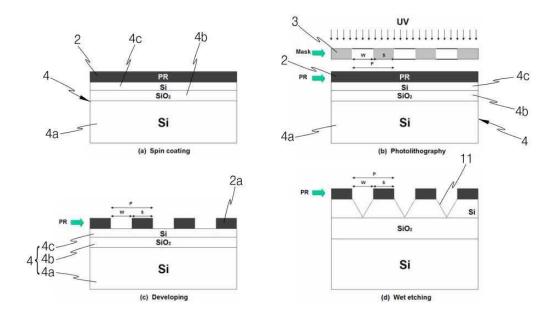

- [0061] 첨부한 도 2는 포토리소그라피와 이방성 식각을 이용하여 V 홈 나노선 배열이 제작되는 공정 흐름도이다. 먼저 단결정 실리콘 기판(1) 위에 PR(2)을 스핀 코팅하고, 이어 90 ~ 95 ℃에서 수 분간 소프트 베이킹(soft baking)한다[도 2의 (a)]. 이후 포토리소그라피 공정을 위해 마스크 정렬기(mask aligner)를 이용하여 광 마스크(3)를 통해 자외선(UV)을 포토레지스트(2)에 조사한다[도 2의 (b)]. UV가 조사된 시료(기판)를 현상하면 도 2의 (c)와 같이 일정한 폭과 간격을 갖는 직선들이 PR 패턴(2a)으로 형성된다. 이후 PR 패턴(2a)을 식각마스크로 사용하여 시료(기판)를 KOH 용액에서 식각하게 된다[도 2의 (d)]. 이때, 반복적인 직선 패턴 사이의 간격은 식각깊이에 의해 결정되는데, 식각깊이가 3 ㎞ 이하로 제한되면 포토리소그라피 공정으로 제조할 수 있는 직선 사이의 간격이 1 ~ 2 ㎞로 정해진다.

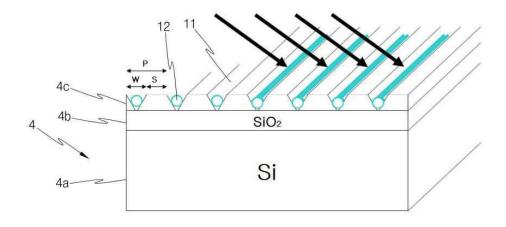

- [0062] 첨부한 도 3은 도 2의 결과로 얻어진 V 홈 배열에 용액 공정으로 나노물질이 정렬된 일 예이다. V 홈(11)의 수는 포토리소그라피용 광 마스크에 의해 1개부터 수백 또는 수천 개까지 필요에 따라 조절될 수 있다. 한 예

로 반복적인 패턴에서 직선의 폭과 직선 사이의 간격이 모두  $1 \mu$ 인 경우 1000개의 V 홈을 만드는데 필요한 직선 배열(array) 폭은  $2 \mu$ 에에 불과하다.

- [0063] 나노물질(12)을 실리콘 V 홈(11)에 정렬하기 위해서는 두 가지 방법이 있다. 첫째는 [문헌 4]의 자기조립 방법을 개선해야 한다. 즉, 도 2의 (c) 단계의 시료를 OTS(octadecyltrichlorosilane) 용액에 담가서 PR이 없는 영역에 증착되도록 한다. 이때, OTS 박막의 두께가 0.5 ~ 1.5 µm 정도가 되기 위해서 [문헌 4]의 담구는 시간보다 훨씬 긴 시간이 필요하다. 이후 시료 표면의 PR 패턴을 아세톤으로 제거하고, OTS 박막을 식각 마스크로 이용하여 실리콘을 KOH 용액 속에서 식각한다. 이어 V 홈이 만들어진 시료를 나노물질이 분산된 용액 속에 넣어 시료의 V 홈에 나노물질이 정렬되도록 한다.

- [0064] 둘째는 첫째 공정에서 OTS 박막을 식각 마스크로 이용하여 V 홈 나노선 배열을 형성한 시료를 APTES(3-aminopropyl trimethoxysilane) 용액에 담가서 박막이 증착되도록 한 뒤 음전하의 작용기를 갖는 SWNT를 용액 공정으로 APTES 박막에 정렬하는 공정 방법이다. 이 공정 방법에서, 시료의 V 홈 내부에 높이에 따라 APTES의 농도가 다른 APTES 박막을 형성한 뒤, 시료를 나노물질 용액 속에 담구어 상기 V 홈의 폭방향으로 한 개의 나노물질이 정렬되도록 한다. 이를 위해 APTES 용액에서 꺼낸 시료를 SWNT 용액에 담구기 전에 평평한 바닥에 놓아두는데, APTES 용액이 V 홈의 내부 벽면을 따라 아래로 흐르기 때문에 APTES의 두께가 아래로 내려가면서 더두꺼워진다. 그 결과 APTES 농도가 더 높은 아래쪽에 SWNT가 배열되므로 단일 SWNT가 배열될 수 있다. 상기 공정에서 APTES 용액에 담구어 APTES 박막을 V 홈에 증착시킨 뒤에는 이를 꺼내서 질소(N2)로 건조시켜 사용한다.

- [0065] 본 발명에서 제안된 상기한 방법은 [문헌 6]에서 사용된 방법과 반대되는 개념이다. [문헌 6]에서는 스탬프에 폴리머를 묻힌 후 스탬프를 찍는 시간을 증가시킨다. 그리고, 폴리머가 확산되는 특성을 이용하여 중심부의 폴리머 농도가 진하고 주변으로 갈수록 약해지는 패턴에 나노물질을 한 개씩 정렬시켰다. 반면에 본 발명에서는 V 홈을 만들어 APTES의 농도가 홈을 따라 아래로 내려가면서 진하게 만든 후 맨 아래쪽에 나노물질을 정렬시키는 방법이다.

- [0066] 다음으로, 포토리소그라피와 이방성 식각을 이용하여 나노선 다중채널 FET를 제조하는 방법에 대해 설명하기로 한다.

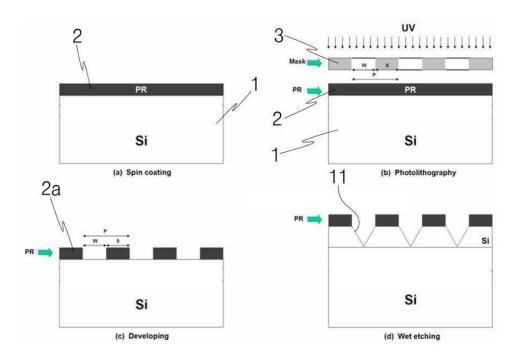

- [0067] 앞에서 설명된 실시예에서, 기판이 실리콘 단결정일 때 나노선 FET 소자를 제조할 수 있는 후 공정이 더 이상 없다. 이에 비해, 이하 설명되는 실시예는 나노선 다중채널 FET를 제작하기 위해 SOI(Si-On-Insulator) 웨이 퍼가 기판으로 사용된 예이다. 첨부한 도 4는 SOI 기판(4) 위에 V 홈(11)을 제작하는 공정도이다. 도 4의 공정도를 참조하면, 기판(4)이 Si 대신에 SOI가 사용된 것을 제외하면 동일하다. 그러나, SOI 기판(4)에서 SiO₂(4b) 위의 Si 박막(4c)은 언도프트(undoped) Si이고 SiO₂(4b) 아래의 Si 기판(4a)은 백-게이트(back-gate) 전극을 만들기 위해 도프트(doped) Si가 사용된다. 또한 KOH 용액의 농도를 30%로 하여 80℃에서 식각하면, (111) 면의 식각률이 0.015 /m/min이 되고, (100)면의 식각률이 1.12 /m/min이 된다. 이 경우 V 홈이 만들어진 후 식각시간을 증가시키면, (111) 면의 식각이 진행되어 아랫면의 SiO₂의 선폭이 증가한다. 이와 같이 본 발명에서 V 홈(11)이 형성되는 식각시간을 측정하여 V 홈이 형성되기 전에 하단면의 선폭을 식각시간으로 조절할 수 있다. 바람직하게는, SOI 웨이퍼를 사용하는 경우, 기판에 형성되는 V 홈은, 깊이방향에 대한 폭방향의 식각비율이 100 이하인 식각용액을 사용하여, V 홈 내부에서 그 하단의 SiO₂가 노출되도록 형성하고, 이때 노출된 SiO₂의 폭을 식각시간으로 조절한다.

- [0068] 첨부한 도 5는 식각용액의 조건을 도 4에서 설명된 조건으로 변경하고 도 3과 동일한 방법으로 V 홈(11)에 나노 물질(12)을 정렬시킨 구조도이다. 물론, 기판(4)이 Si 대신에 SOI로 바뀌었다.

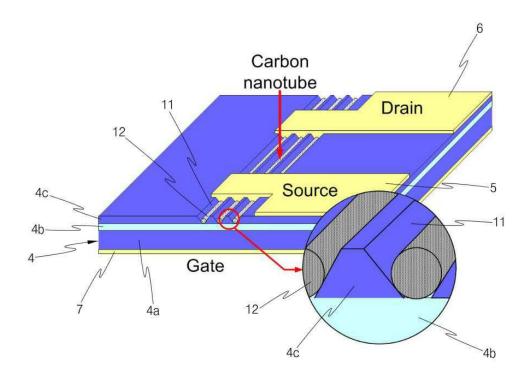

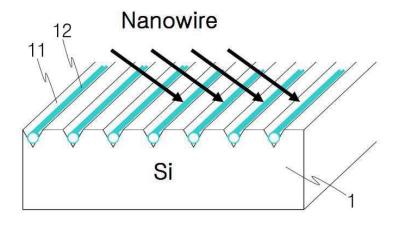

- [0069] 첨부한 도 6은 V 홈에 나노물질이 정렬된 나노선 다중채널 FET 소자의 개념도이다. 복수의 V 홈(11) 나노선에 각각 나노물질(12)이 정렬되어 다중채널이 구성되고, 이 다중채널을 사이에 두고 소스 전극(5)과 드레인 전극 (6)이 형성되며, 기판(4)의 배면에는 백-게이트 전극(7)이 형성되어, V 홈 FET 소자가 제조될 수 있다. 도 6을 참조하면, 나노물질(12)의 아랫면 부분은 SiO<sub>2</sub>(4b) 위에 접촉하고, 양쪽 측면 부분은 도핑되지 않은 (undoped) Si 박막(4c)에 접촉되어 있다. 따라서, 이웃하게 정렬된 나노물질(12)은 전기적으로 고립되어 있게된다.

- [0070] 도 6에서 FET 소자의 채널이 세 개인데, 채널의 수는 도 5와 같이 여러 개가 되는 V 홈 나노선 다중채널 FET 소자의 제조도 가능하다. 각각의 채널에는 폭방향으로 한 개의 나노물질이 정렬된다. 그러므로, V 홈 나노선

다중채널 FET 소자는 단 한 개의 나노튜브로 제작된 단일채널 FET 소자보다 큰 전류를 운반할 수 있을 뿐만 아니라, SWNT의 무작위 네트워크(random network)를 이용한 FET 소자보다 큰 전하 이동도를 얻을 수 있다. 그결과, 기존의 단일채널 FET 소자와 네트워크 FET 소자의 단점들이 모두 동시에 해결될 수 있는 기술이 본 발명에서 제공된다.

- [0071] 이와 같이 하여, 본 발명은 대면적과 저비용으로 나노선 배열을 제조할 수 있는 포토리소그라피와 식각기법의 반도체 기술과 용액 공정으로 나노선 배열을 구성하는 단위 나노선의 폭방향으로 한 개의 나노물질이 정렬되는 나노 기술이 융합된 V 홈 나노선 다중채널 FET 소자의 제조 방법을 제공할 수 있게 된다. 특히, 포토리소그라 피와 식각기법은 기존의 실리콘 반도체 산업과 호환성이 있기 때문에 저비용으로 대량생산이 가능한 장점이 있다. 또한 용액 공정은 특별한 고가의 장비 없이 쉽게 대면적으로 공정을 할 수 있기 때문에 공정비가 저렴하다. 따라서, 본 발명은 V 홈 나노선 다중채널 FET 소자나 FET 소자를 기반으로 하는 나노선 다중채널 FET 어레이(array) 소자 및 상기 소자들과 구동회로가 집적된 SOC(System On Chip) 칩을 대량생산 방식으로 제조할 수 있는 방법을 제공하며, 산업상으로 이용 가능성이 매우 크다.

- [0072] (참고)

- [0073] [문헌 5] H. Seidel, L. Csepregi, A. Heuberger, and H. Baumgartel, "Anisotropic Etching of Crystalline Silicon in Alkaline Solutions," *J. Electrochem. Soc.*, Vol. 137, No. 11, pp. 3612-3626(1990).

- [0074] [문헌 6] Sung Myung, Jiwoon Im, Ling Huang, Saleem G. Rao, Taekyeong Kim, Dong Joon Lee, and Seunghun Hong, ""Lens" Effect in Directed Assembly of Nanowires on Gradient Molecular Patterns," *J. Phys. Chem. B, Vol. 110, No. 21*, pp 10217 10219(2006).

#### 도면의 간단한 설명

- [0075] 도 1은 본 발명에서 GaAs와 Si 단결정의 이방성 식각을 보여주는 도면,

- [0076] 도 2는 본 발명에서 포토리소그라피와 이방성 식각을 이용하여 V 홈 나노선 배열이 Si 기판 위에 제작되는 공정 흐름도,

- [0077] 도 3은 Si 기판 위에 제조된 V 홈 나노선 배열에 용액 공정으로 나노물질이 정렬된 도면,

- [0078] 도 4는 SOI 기판 위에 V 홈이 제작되는 공정도,

- [0079] 도 5는 다중 V 홈에 나노물질이 정렬된 구조도,

- [0080] 도 6은 SOI 기판 위에 제작된 V 홈 나노선 FET 소자의 구조도.

- [0081] <도면의 주요 부분에 대한 부호의 설명>

- [0082] 1, 4 : 기판 11 : V 홈

- [0083] 12 : 나노물질

## 도면

## 도면1

### 도면2

## 도면3

## 도면4

## 도면5

# nanowire

## 도면6